# INTERFACE STANDARD & DESIGN GUIDE

for TI 99/4A PERIPHERALS

TONY LEWIS, PE

(C) 1989, ALL RIGHTS RESERVED

# DISCLAIMER ON CONTENTS

The following should be read and understood before purchasing and/or using this Interface Standard/Design Guide.

The technical information contained in this document is accurate, to the best of the knowledge of the author and the reviewers. However, given the volatile nature of the computer and electronics industry, along with the lack of access to original design documentation on the 99/4A system, there is no warranty that the contents of this manual will be free from error or will meet the specific requirements of the purchaser. The purchaser assumes complete responsibility for any decision made or actions taken based on information obtained using the contents of this manual. Any statements made concerning the utility of the contents are not construed as expressed or implied warranties.

The author reserves the right to revise any of the contents at any time without notice. However, registered owners will be notified if significant revisions or additions to the contents are made. Purchasers are encouraged to notify the author of any errors found in the text or graphics.

The author makes no warranty, either expressed or implied, including but not limited to any implied warranties of fitness, operability, or validation of design, regarding the contents or any information derived therefrom, and makes all contents available solely on an "as is" basis.

In no event shall the author or the reviewers be liable to anyone for special, collateral, incidental, or consequential damages in connection with or arising out of the purchase or use of this literature and the sole and exclusive liability of the author, regardless of the form of the action, shall not exceed the purchase price of this manual. Moreover, the author shall not be liable for any claim of any kind whatsoever by any other party against the user of this manual.

Texas Instruments did not contribute to, commission, nor approve the creation of the Interface Standard/Design Guide. All information used in deriving the contents of this manual are available in the public domain. "TI", "TI 99/4A", and "99/4A" are registered trademarks of Texas Instruments.

# NOTICE OF USER REGISTRATION

Each copy of this document has a unique identification number assigned to it, which is printed on an adhesive label and attached to the manual cover. The Purchaser must forward a postcard or letter listing his/her name, address, and document ID number to the address given below. The Purchaser then becomes the only authorized User of the manual. All inquiries made to the author by the User must include the ID number of the manual; inquiries without the User's name and manual ID number will not receive a response. Registered Users will receive notices of future significant revisions to the manual as they are released by the author. All readers of the manual are strongly encouraged to provide comments, criticisms, or input on errors concerning the manual directly to the author:

Tony Lewis 409 Drolmond Dr. Raleigh NC 27615

#### REFERENCES

The following sources were used as references for this manual:

- 1. Microprocessors/Microcomputers System Design, Texas Instruments, McGraw-Hill Book Company, 1980. QA76.S.T49. ISBN 0-07-0637558-X.

- 2. 16 Bit Microprocessor Systems, Texas Instruments, McGraw-Hill Book Company, 1982. TK7895.M5.C35. ISBN 0-07-063760-1.

- 3. TI 99/4A Console and Peripheral Expansion System Technical Data, Texas Instruments, 1983.

- 4. Hardware Manual for the TI 99/4A Home Computer, Micheal Bunyard, PE, 1986.

- 5. TMS9900 Data Manual, Texas Instruments, 1985.

- 6. TTL Cookbook, Don Lancaster, Howard Sams Co., 1974. ISBN 0-672-21035-5.

- 7. TI 99/4A Peripheral Schematics: RS232-1039308; Memory Expansion-1039330, Disk Controller-1039340.

- 8. Software Development Handbook, 2nd Edition, Texas Instruments, 1981. ISBN 0-904047-31-8.

- 9. TI 99/4A INTERN, Heiner Martin, Verlag für Technik und Handwerk GmbH, 1985. ISBN 3-88180-009-3.

- 10. Explorer Technical Manual, Millers Graphics, 1985.

- 11. DiskAssembler Technical Manual, Millers Graphics, 1986.

- 12. PEB ProtoBoard Manual, Scott Coleman and John Willforth, 1988.

- 13. Technical Drive, Monty Schmidt, 1987.

- 14. Editor/Assembler Manual, Texas Instruments, 1982.

- 15. Texas Instruments Graphics Programming Language User's Guide, Personal Computer Division, Texas Instruments, Dec. 1979.

- 16. Horizon RAMDisk Source Code and Technical Manual, Horizon Computer Limited, 1986.

#### RESOURCES

This document was created on TIWriter Version 4.2, by R. A. Green Software. Graphics were created with AutoSketch 2.0.

Disassembly of existing console and DSR code was accomplished via Millers Graphics EXPLORER and DISKASSEMBLER programs. The program "GPLDIS" was used to disassemble the GPL code in GROMs 0-2. Reference 9 provided input on console routines. References 9, 10, and 14 were used to compile information on use of console RAM locations as they pertain to DSRs.

References 1, 2, 4, and 5 provide information on the TMS9900 microprocessor and related system design. References 1, 8 and 14 are excellent sources on assembly programming. Reference 13 provides completely disassembled and commented DSR codes for several peripherals. Reference 15 provides information on the Graphics Programming Language, which was useful in disassembling code in GROMs 0-2.

All references listed are recommended as excellent sources of information for the 99/4A and its Peripheral Expansion System, and the reader is encouraged to consult them for more information. Where possible, consult with the local library about obtaining references via the InterLibrary Loan System, using the ISBN number. Below is a list of current addresses for some of the references:

Millers Graphics 1475 W. Cypress Ave. San Dimas, CA 91773

Texas Instruments Inc. Data Book Marketing PO Box 117692 Carrollton, TX 75011-7692 (800) 232-3200

The Bunyard Group PO Box 62323 Colorado Springs, CO 80962-2323

LL Conners Enterprises Computer and Electronics 1521 Ferry Street Lafayette, IN 47904

Readers interested in obtaining copies of Technical Data and the GPL manual may contact the author directly for more information.

#### UTILITY PROGRAMS

A 5-1/4" single sided, single density diskette containing utility programs is provided with the manual to assist the peripheral developer in creating DSRs and application programs. The purpose of including these programs with the manual is to provide (in the author's opinion) the "best" utility programs available to the developer such that DSRs may be quickly written, debugged and released. Disassemblers are also included for reverse engineering console/peripheral code as needed to insure compatibility. [Use of Millers Graphics DISKASSEMBLER for disassembly is highly recommended; DISKASSEMBLER is available from several sources.]

Each of the programs took several days of development by their authors to complete. Responsible purchasers are obligated to forward a contribution to the software authors to acknowledge the usefulness of their products, and to encourage development of future products.

HOTBUG is not fairware; consult the documentation for proper registration of ownership. The README file on the disk contains a list of the utility programs, program description, recommended contribution amount, author name and current address.

# TABLE OF CONTENTS

# TABLE OF CONTENTS

| SE | CTION                                                                                                                                                           | <u>PAGES</u>                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Α: | 9900 SIGNAL/INTERFACING 1.0 Introduction 2.0 Memory Bus 3.0 CRU Bus 4.0 Interfacing with the /4A                                                                | A1-A6<br>A1<br>A1<br>A2<br>A3     |

| В: | CONSOLE (44 PIN) AND PROX (60 PIN) CONNECTORS 1.0 Introduction 2.0 Console 44 Pin Connector 3.0 PBox Bus Signals - 60 Pin Connector 4.0 General Notes           | B1-B5<br>B1<br>B1<br>B2<br>B4     |

| C: | PBOX CARD ELECTRONIC FEATURES 1.0 Introduction 2.0 Interfacing Notes 3.0 General Notes on Buffering, Activation and Misc. Signals 4.0 Peripheral Polling System | C1-C12<br>C1<br>C1<br>S C8<br>C11 |

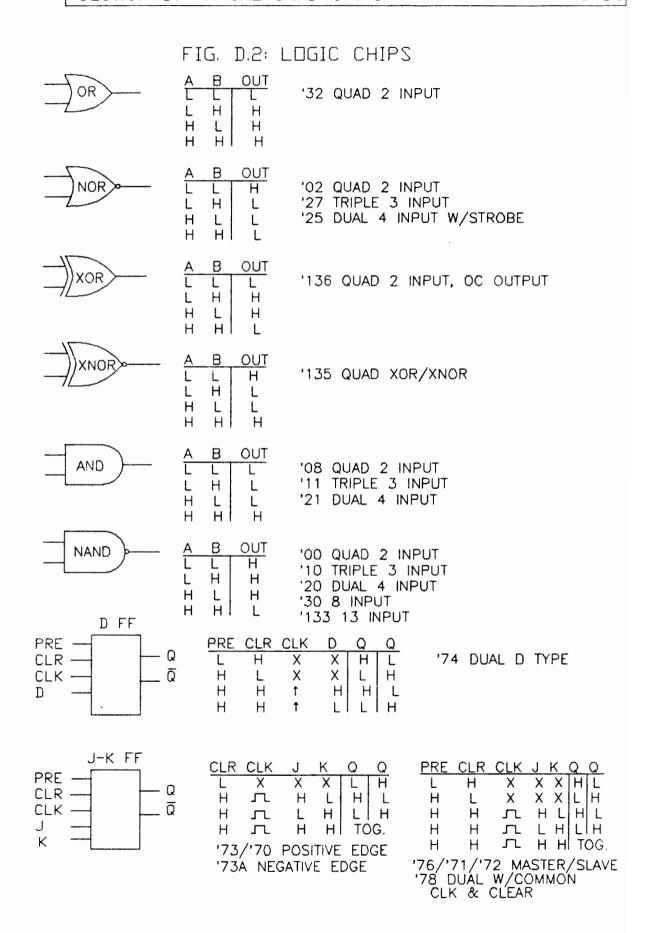

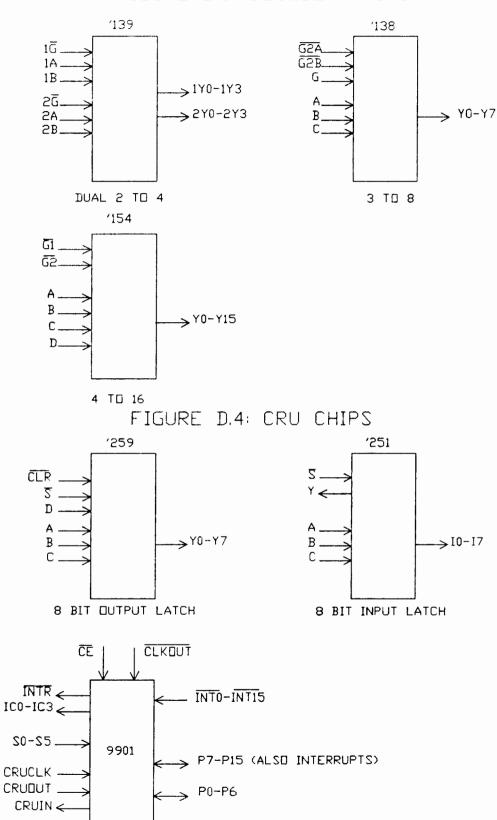

| D: | TYPICAL CARD CHIPS 1.0 Introduction                                                                                                                             | D1-D4<br>D1                       |

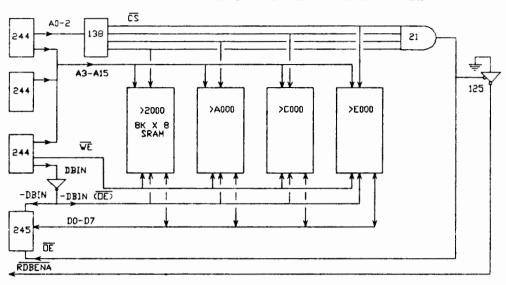

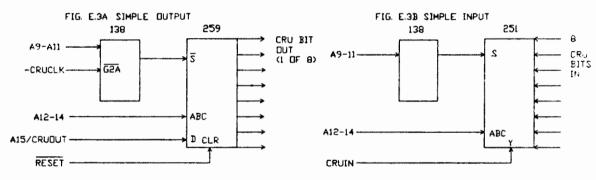

| E: | TYPICAL CIRCUIT EXAMPLES 1.0 Introduction 2.0 Memory Interface 3.0 CRU Interface 4.0 Memory Mapped Interface                                                    | E1-E5<br>E1<br>E1<br>E1<br>E2     |

| F: | TI DEVELOPED CARDS 1.0 Introduction 2.0 RS232 Card 3.0 32K Memory Card 4.0 Disk Drive Controller Card                                                           | F1<br>F1<br>F1<br>F1              |

| G: | PERIPHERAL LOCATION ASSIGNMENTS 1.0 Introduction                                                                                                                | G1-G3<br>G1                       |

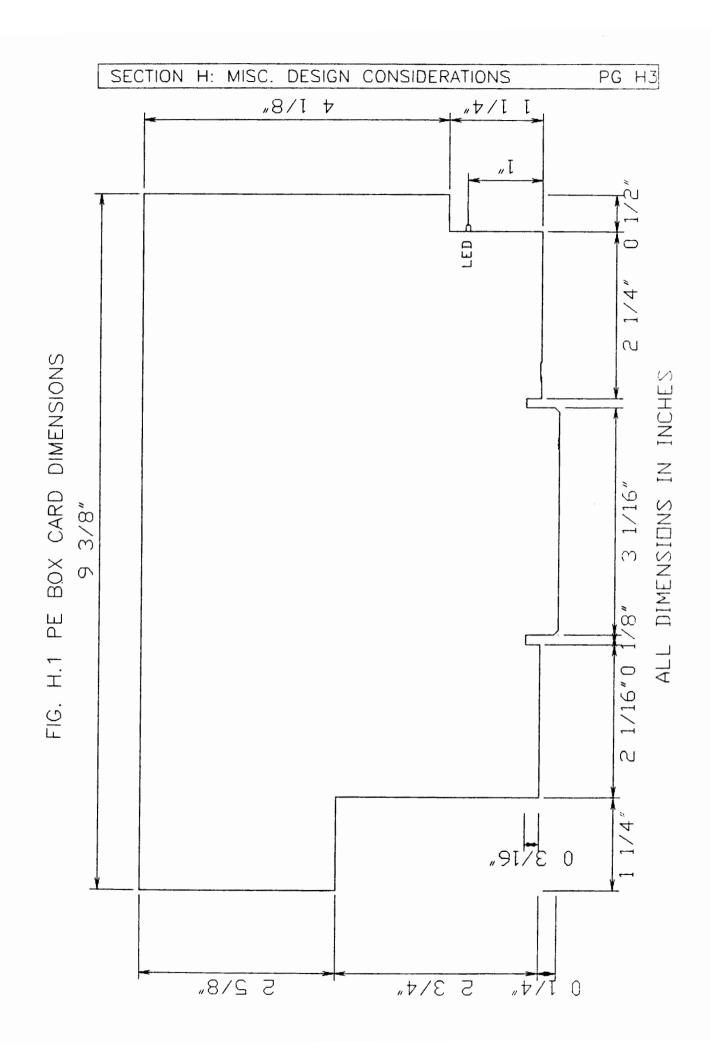

|    | MISCELLANEOUS DESIGN CONSIDERATIONS 1.0 PBox Peripheral Card Dimensions and Layout 2.0 Prototype Board 3.0 Extender Cable 4.0 Modified Interface Card           | H1-H4<br>H1<br>H1<br>H2<br>H2     |

# TABLE OF CONTENTS

| SECTION                                                                                                       | PAGES                     |

|---------------------------------------------------------------------------------------------------------------|---------------------------|

| I: DSR ARCHITECTURE 1.0 Introduction 2.0 Device Service Routines                                              | I1-I33<br>I1<br>I1        |

| J: DSR ACCESS 1.0 Introduction 2.0 Console DSR Access 3.0 XBASIC DSRLNK                                       | J1-J24<br>J1<br>J1<br>J15 |

| K: MISCELLANEOUS ACCESS NOTES 1.0 Introduction 2.0 Direct Access 3.0 Notes on PARs and File Management System | K1-K5<br>K1<br>K1         |

# INTRODUCTION

The purpose of this manual is to consolidate all information available in the public domain on the design and development of peripherals for the TI 99/4A computer into one reference. There are several excellent documents on the hardware and software of the console and its peripheral system available; however, this manual has been specifically written for designer/developers who wish to create new hardware and/or software for TI 99/4A peripherals.

The manual is an intermediate level text in that it is assumed that the reader is familiar with the TMS9900, its assembly language, the 99/4A peripheral system, the File Management System, and general computer and electronics concepts. Readers who are novices in any of these areas should consult the appropriate references before using this manual. Although some overlap of information exists between this manual and the references, the reader is urged to consult the references as needed for information not included in the Interface Standard/Design Guide.

As the title implies, this manual is meant to provide a consistent basis, or standard, for designers to create peripherals that will be compatible not only with the TI 99/4A, but with other peripherals as well. Basic information on hardware and software techniques is also provided for use by the developer.

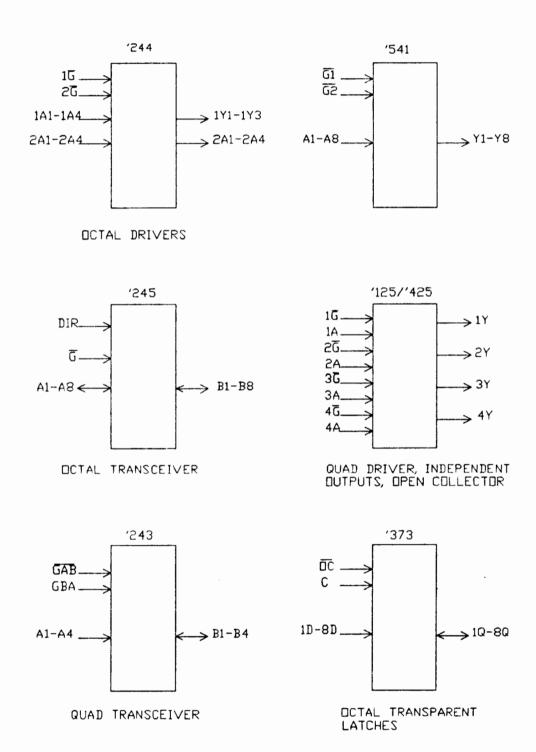

Sections A-H cover the hardware aspects of the console and peripherals, and includes design information on chips and circuits. New peripheral types are defined in Section C, and existing peripheral locations are assigned in Section G. Section I covers the basics of Device Service Routine (DSR) construction. Section J discusses how the routines built into the console access peripherals and their DSRs. Where ever possible, examples are given of hardware and software concepts to assist the reader.

The author hopes that all readers will find the Interface Standard/Design Guide useful and informative. The author would also like to thank the following people who reviewed and commented on the original draft of the manual:

John Willforth Matt Beebe Jim Reiss Peter Hoddie Paul Carlton Mike Dodd Barry Boone Mid-Atlantic 99ers John Johnson

|  | • |                                                                                                               |

|--|---|---------------------------------------------------------------------------------------------------------------|

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   | `\                                                                                                            |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   | l                                                                                                             |

|  |   | 1                                                                                                             |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   | i de la compansa de |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   | -                                                                                                             |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   | •                                                                                                             |

|  |   |                                                                                                               |

|  |   | ä                                                                                                             |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

|  |   |                                                                                                               |

# SECTION A: 9900 SIGNALS/INTERFACING

# 1.0 <u>Introduction</u>

The TMS9900 microprocessor has 64 pins, 49 of which are used as signals to communicate with other chips and the outside world. These signals can be grouped into two basic sets, or buses: memory bus and CRU bus. The memory bus can be further divided into three types of signals: address, data, and control. This section will briefly discuss the function of the TMS9900 signals, and how they are used and modified by the /4A system. References 1, 2, and 5 contain more detailed descriptions of the 9900 signals.

# 2.0 Memory Bus

The memory bus is used to communicate with memory chips (or memory mapped devices) by selecting an address, then reading or writing data to or from the address. The address bus provides signals to select individual addresses, while the data bus provides a two way communication path for information to travel. The control bus signals coordinate action between the microprocessor and other devices. Below is a brief description of the functions of the memory bus.

#### 2.1 Address Bus (AO-A14)

The 9900 has 15 address signals, A0 - A14, with A0 the most significant bit (MSB). These signals are driven out of the micro, and are used to select the address of information to be read or written. It is assumed that the memory system will have a 16 bit word design, and not a byte (8 bits) wide data bus, because the 9900 addresses 32K words (16 bits) for each read or write function. The 9900 cannot address individual bytes because there is no A15 signal to discriminate between even and odd bytes. To perform byte reads, the 9900 will read two bytes simultaneously, discarding the information in the unused byte. To perform byte writes, the 9900 first reads two bytes, alters the byte being written to, and then writes both bytes back to memory.

#### 2.2 Data Bus (D0-D15)

The data bus is 16 bidirectional signal lines used to read or write information from other devices. Since the data bus is 16 bits wide instead of eight, the 9900 can access twice as much information per unit of time than a similar micro with an 8 bit data bus.

#### 2.3 Control Signals (DBIN, -WE, etc.)

Control signals are used to synchronize the operations of the 9900 with the devices that it is communicating with. The 9900 control signals are summerized below; consult Reference 1 or 5 for more detail

on these signals.

|        | in   |                  |                                                                                        |

|--------|------|------------------|----------------------------------------------------------------------------------------|

| 1/0    | /4A? | Signal           | Description                                                                            |

| 0      | Y    | Signal<br>-MEMEN | used to enable memory accesses, differentiates between memory bus and CRU bus activity |

| 0      | Y    | DBIN             | data bus direction, determines the direction of data (in or out) for the 9900          |

| 0      | Υ    | -WE              | write enable, denotes writes to memory                                                 |

| 0      | Υ    | IAQ              | Instruction Acquisition Status, denotes that                                           |

|        |      | •                | the microprocessor is obtaining an instruction from memory                             |

| I      | Υ    | READY            | memory ready status, informs micro that                                                |

| -      | •    |                  | system memory is ready to be accessed.                                                 |

| 0      | N    | WAIT             | Ready acknowledge, status signal that 9900                                             |

| •      |      |                  | acknowledges memory not ready to be accessed.                                          |

| I      | N    | -HOLD            | HOLD process, when active, puts 9900 signals                                           |

| _      |      |                  | in inactive state. Memory bus may now be                                               |

|        |      |                  | driven by another device.                                                              |

| 0      | Υ    | HOLDA            | HOLD Acknowledge, informs external device that                                         |

|        |      |                  | 9900 acknowledges receipt of HOLD request.                                             |

| I      | Υ    | -RESET           | Reset input, resets micro to initial state                                             |

| I<br>I | Υ    | -LOAD            | nonmaskable interrupt, forces 9900 to branch                                           |

|        |      |                  | to address >FFFC for new program counter and                                           |

|        |      |                  | workspace values                                                                       |

| I      | N    | ICO-IC3          | interrupt code 0-3, inputs for up to 16                                                |

|        |      |                  | maskable interrupts                                                                    |

| I      | Υ    | -INTREQ          | Interrupt Request, informs 9900 that an                                                |

|        |      | ·                | interrupt code is valid on ICO - IC3                                                   |

[signals may be either available externally, or used only internally by the console; signals may be altered or unused in current design]

# 3.0 CRU Bus

The input/output bus on the 9900 is known as the Communication Register Unit (CRU) bus. The CRU bus is similar in concept to the memory bus, with the following exceptions:

- 1: The memory bus can communicate in words (16 bits) with a set of odd and even addresses. The CRU bus associates <u>one bit</u> per address accessed by the 9900.

- 2: The CRU address space is limited to >0000 to >1FFF, where as the memory bus can address >0000 to >FFFF. These are separate and distinct addresses; control signals are used to differentiate between memory address space and CRU address space.

- 3: The CRU bus is used primarily to control peripherals (on/off) versus communication of data because the memory bus transfers more bits per access than the CRU bus.

- 4: The CRU bus does not have as many control signals as the memory bus, sometimes causing design concerns when developing

circuitry.

The CRU bus consists of the following signals, all of which are used in the /4A system:

A3-A14 (out) These lower order address lines define the CRU space >0000 to >1FFF. Same lines as used by memory bus.

CRUCLK (out) CRU Clock, used during CRU output to inform external device that address bus and CRUOUT output bit signals are stable.

CRUOUT (out) CRU Output Data, outputs value of bit when CRUCLK

is active.

<u>CRUIN</u> (in) CRU Input Data, inputs bit value into 9900

References 1 and 2 have excellent discussions of the CRU bus as implemented by the 9900.

# 4.0 Interfacing with the /4A

The signals available for the 9900 are used in various combinations to allow it to interface to external devices. This section will cover the relationships between the signals on the memory and CRU buses as they are presented to peripheral devices by the /4A system. Not all 9900 signals are available in the /4A system for use with peripherals; likewise, the relationship and timing of some signals are radically modified by the /4A system and do not conform to the original 9900 signal format. Most notable is the fact that the /4A system has an 8 bit peripheral data bus, not 16 bits.

### 4.1 Memory Bus Interfacing

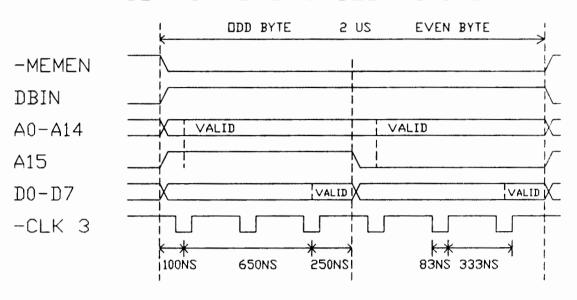

The /4A system will read an odd and even byte within a word boundary by reading the odd byte first, then the even one. Control logic circuitry internal to the /4A allows it to read the first byte, then the second, and then reassembles them into a word before presenting it to the 9900. Figure A.1 shows the appropriate signal timing and relationships.

The control logic is:

IF -MEMEN is low AND DBIN is high, THEN a memory READ is occuring.

There is no need to include -WE in decoding for a Read. The /4A system automatically inserts two wait states (333 ns each) for each byte access. Allowing for 100 ns settling time for the address lines to become valid after -MEMEN goes low, a peripheral has up to 650 ns to provide valid data on the data bus.

A0-A14 are held constant per memory read - - - only A15 changes state during a memory access for a Read. A15 is generated by the /4A system to differentiate between odd and even bytes, and is not produced by the 9900.

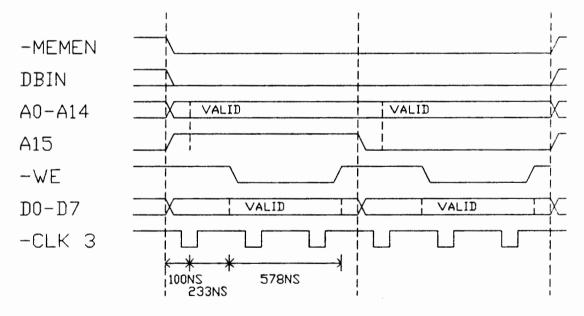

The /4A system writes information to an odd and even byte within a word boundary with timing similar to a Read operation. Figure A.2 shows signal timing and relationships for a Write operation. The control signal logic is:

IF -MEMEN is low AND DBIN is low, THEN a memory Write is occuring.

Data on DO-D7 is valid when -WE goes low.

Data is presented on the data bus and is valid (-WE goes low) approximately 333 ns after -MEMEN and DBIN are both low; -WE remains low for 578 ns, typically. One -WE pulse is generated per byte Write, whereas the 9900 generates only one -WE pulse per word. Recall also that the 9900 always performs a Read operation to a word boundary prior to a Write operation; this is true of the /4A system also (iethe /4A reads two consecutive bytes, even when performing a single byte write operation).

#### 4.2 CRU Bus Interfacing

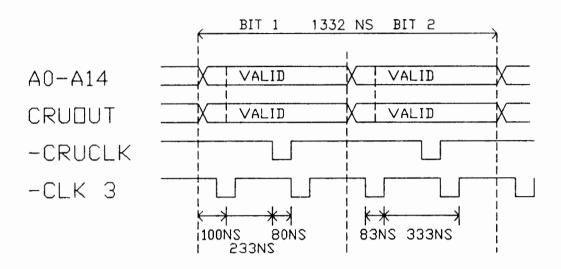

Input and output on the CRU bus is more simplistic but also can create problems for designers if certain relationships are ignored. The CRUCLK signal of the 9900 is inverted by the /4A system to produce -CRUCLK. This is used to strobe a CRU bit out of the /4A via the CRUOUT line, similar to the way -WE strobes data from the DO-D7 lines. The timing relationship fo a CRU output series is shown in Figure A.3. The control signal logic is:

IF -MEMEN is high AND -CRUCLK is low THEN a CRU bit is output on CRUOUT.

The -MEMEN signal allows the /4A to multiplex the A15 and CRUOUT on the same pin; the pin is for "A15" if -MEMEN is low, and for "CRUOUT" if -MEMEN is high.

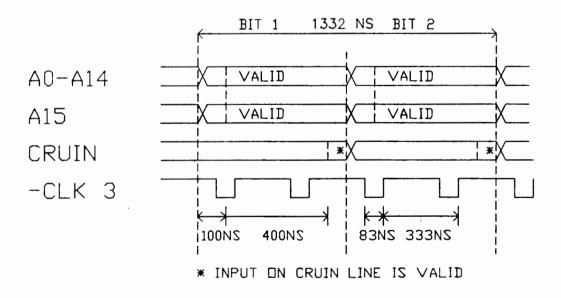

Input on the CRU bus is accomplished by establishing a valid address on AO-A15, then reading the bit value on the CRUIN line 400 ns after the address is valid.

No other control signals are needed to define a CRU Read operation. Unlike the memory bus operation, external devices have no warning that an operation on the CRU bus is about to occur (-MEMEN going low notifies the system that a memory bus is going active; there is no corresponding "-CRUEN" signal). Designers of peripherals utilizing the CRU bus must be aware of this restriction.

FIG A.1: READ CYCLE TIMING

FIG. A.2: WRITE CYCLE TIMING

FIG. A.3: CRU DUTPUT

FIG. A.4: CRU INPUT

SECTION B: CONSOLE (44 PIN) AND PBOX (60 PIN) CONNECTORS

# 1.0 Introduction

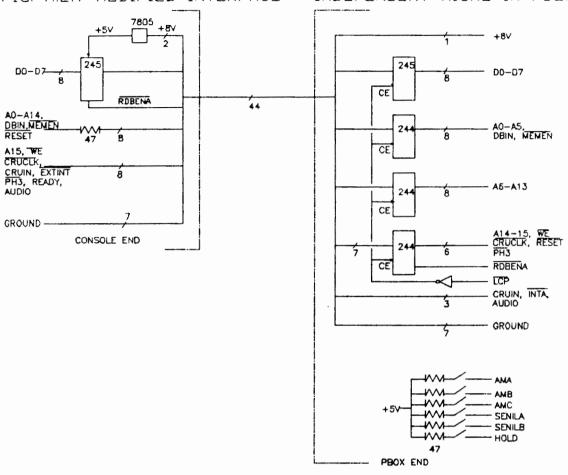

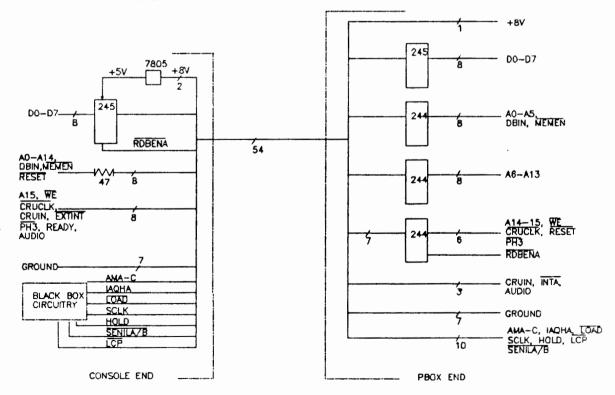

Not all of the signals from the 9900 are made available to the outside peripherals. The side connector on the console has 44 pins, 38 of which are signals (the rest are power and ground pins). The PBox bus has a 60 pin connector, which has 12 power and ground pins, 7 unused (currently) signals, and 41 active signals. The signals for the console and PBox are listed below, along with comments of their intended functions. Figures B.1 and B.2 show the console and PBox connectors as viewed looking into the connector.

# 2.0 Console 44 Pin Connector

The side connector on the console is an edgecard type with 44 pins spaced 0.10" pin to pin spacing. The signals, functions and pin numbers are as follows:

| Signal<br>AO (MSB)<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15/<br>CRUOUT | Pin<br>31<br>30<br>20<br>10<br>7<br>5<br>29<br>17<br>14<br>18<br>6<br>8<br>11<br>15<br>16 | 1/0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Comments Address bus signals  " " " " " " " " " " " " " " A15 is created by logic internal to the console, not by the CPU. CRUOUT is gated A15, and is not active unless -MEMEN is high. |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DO<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6                                                                                        | 37<br>40<br>39<br>42<br>35<br>38<br>36<br>34                                              | I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0         | Bidirectional data bus " " " " " " " " "                                                                                                                                                 |

| <u>Signal</u><br>-MEMEN<br>DBIN | Pin<br>32<br>9 | 1/0<br>0<br>0 | Comments Same as for 9900                                                                                                                                                          |

|---------------------------------|----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -WE                             | 26             | 0             | This is highly modified from the original 9900 signal into two active low -WE signals per cycle (one per byte)                                                                     |

| -MBE                            | 28             | 0             | Memory Block Enable. Created by console logic; device enable signal for the >4000->5FFF memory block. Convenient for side mounted peripherals. Signal not transmitted to PBox bus. |

| -CRUCLK                         | 22             | 0             | Phase 3 clock, inverted                                                                                                                                                            |

| CRUIN                           | 33             | I             | Same as for 9900                                                                                                                                                                   |

| READY                           | 12             | I             | " , with pull up resistor                                                                                                                                                          |

| IAQ                             | 41             | 0             | Not transmitted to PBox bus                                                                                                                                                        |

| -LOAD                           | 13             | I             | <b>"</b>                                                                                                                                                                           |

| -RESET                          | 3              | 0             | This is output, and cannot be used to input a -RESET signal                                                                                                                        |

| -EXT INT                        | 4              | I             | External Interrupt, active low, used by peripherals to indicate an interrupt request to the 9900                                                                                   |

| -PH 3                           | 24             | 0             | Phase 3 of the 9900 4 phase clock, inverted to active low.                                                                                                                         |

| SBE                             | 2              | 0             | Speech Block Enable; indicates access to speech memory at >9000/>9400                                                                                                              |

| AUDIO IN                        | 44             | I             | Input for audio from speech module to sound chip                                                                                                                                   |

| +5V<br>-5V                      | 1<br>43        |               | Supply voltage for speech module                                                                                                                                                   |

|                                 |                |               | *Not connected to PBox or interface cable.<br>DO NOT use for side peripherals, or damage<br>to console power supply may occur.*                                                    |

| GROUND                          | 21,2           | 23,25,27      | Ground                                                                                                                                                                             |

# 3.0 PBox Bus Signals - 60 Pin Connector

The PBox bus uses 60 pin female connectors with pins spaced 0.10" pin to pin spacing. Not all of the signals available from the 44 pin connector are available in the PBox bus. The Interface Card sold with the PBox determines which signals were transferred. The PBox end of the cable also holds some (currently) unused signals high, by tieing them to a 5V source via a resistor. The signals, functions, and pin numbers are as follows:

| Signal<br>A0.A<br>A1.A<br>A2.2<br>A3.A<br>A4.A<br>A5.A<br>A6.A<br>A7.A<br>A8.A<br>A9.A<br>A10.A<br>A11.A<br>A12.A<br>A14.A<br>A15/<br>CRUOUT.A | Pin<br>43<br>44<br>41<br>42<br>39<br>40<br>37<br>38<br>35<br>36<br>33<br>31<br>32<br>29<br>30 | I/0* I I I I I I I I I I I I I I I I I I I    | Comments Address bus signals; "A" suffix denotes PBox signal " " " " " " " " " " " " " " " " " " "                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| AMA.A<br>AMB.A<br>AMC.A                                                                                                                        | 46<br>45<br>48                                                                                | HIGH<br>HIGH<br>HIGH                          | Extended address bit, held high by interface card                                                                                        |

| DO<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7                                                                                                   | 28<br>25<br>26<br>23<br>24<br>21<br>22                                                        | I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0 | Data bus signals "" "" "" "" "" "" "" "" "" "" "" "" ""                                                                                  |

| -MEMEN.A DBIN.A -WE.A -CRUCLK.A CRUIN READY.A IAQHA                                                                                            | 56<br>52<br>54<br>51<br>55<br>4                                                               | I<br>I<br>I<br>I<br>O<br>O<br>N/C             | Same as 44 pin side port signals " " " " " IAQ and Hold Acknowledge gated together. For use with 9995 based machines as Hold Ack.        |

| -LOAD<br>-RESET<br>-INTA<br>-CLKOUT<br>AUDIO                                                                                                   | 18<br>6<br>17<br>50<br>10                                                                     | N/C<br>I<br>O<br>I<br>O                       | Not used with /4A  -EXT INT -PH 3                                                                                                        |

| SCLK<br>-LCP                                                                                                                                   | 8<br>9                                                                                        | N/C<br>N/C                                    | System clock. Use is not defined with /4A<br>9995 indicator. Low=9995 machine, high=/4A.<br>Possible use to switch peripherals to faster |

| PCBEN<br>-HOLD                                                                                                                                 | 12<br>13                                                                                      | HIGH<br>N/C                                   | speed.<br>Enables cards in PBox. Low disables all cards.<br>Active low HOLD request for 9995 based machines                              |

| Signal                           | Pin          | 1/0*              | Comments                                                                                                                                                                                                                               |

|----------------------------------|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -SENILA                          | 15           | HIGH              | Interrupt level A and B Sense Enable. Allows                                                                                                                                                                                           |

| -SENILB                          | 16           | HIGH              | computer to quickly identify peripheral interrupt. Not used by /4A system.                                                                                                                                                             |

| -RBDENA                          | 11           | 0                 | Active low remote data bus driver enable line. Each peripheral that utilizes the DATA bus must generate an -RDBENA signal when accessing the data bus. This signal enables the LS245 transciever in the console end of interface card. |

| GROUND                           |              | ,7,20,27<br>49,53 | Ground                                                                                                                                                                                                                                 |

| UNREG 8V<br>UNREG -1<br>UNREG +1 | 1,2<br>6V 57 | ,58               | Used to supply unregulated voltages to voltage regulators mounted on peripheral cards.                                                                                                                                                 |

[\*Either <u>input</u> into the PBox bus, or <u>output</u> to the console]

# 4.0 General Notes

- 4.1 The interface cable shares a common ground between the console and PBox. Positive and negative voltages are not interconnected between the PBox and the 44 pin console connector.

- 4.2 -RBDENA is not needed for peripherals that do not use the data bus (DO-D7). If used, it should be active low with the chip enable signal for the data bus transciever for the peripheral.

- 4.3 Unregulated +8V, +16V, and -16V sources are provided to allow for voltage regulators (as needed) on each peripheral card. Temporary voltage transients on an individual card will not affect the other peripheral cards.

- 4.4 Signals held high (+5V) by the Interface Card cannot be used unless the Interface Card is removed, modified or replaced with a different interface card.

FIG. B.1: 44 PIN SIDE EDGEBOARD CONNECTOR (VIEW LOOKING INTO CONSOLE SIDE)

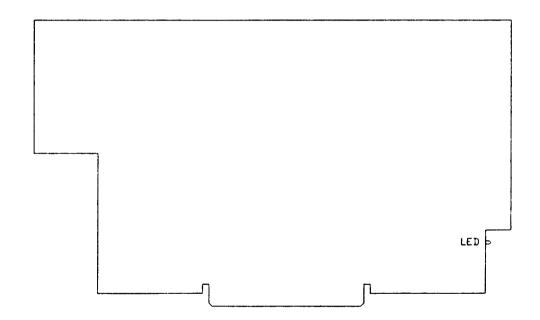

FIG B.2: 60 PIN PBOX CONNECTOR SOCKET

```

2

+8V

1

+8V

GROUND

3

4

READY.A

5

7

GROUND

6

-RESET

GROUND

8

SCLK

9

-LCP

10 AUDIO

-RDBENA

11

12 PCBEN

HOLD

13

14 IAQHA

15

-SENILA

16 -SENILB

17

-INTA

18 -LOAD

D7

19

20 GROUND

D5

21

22 D6

25

ND 27

1.A 29

1.A 31

1.A 33

1.A 33

1.A 33

1.A 35

1.A 36

1.A 36

1.A 36

1.A 36

1.A 36

1.A 36

1.A 37

1.A 40

1.A 42

1.A 40

1.A 41

1.A 46

1.A 48

1.A

23

D3

24 D4

GROUND

A14.A

30 A15/CRUOUT

A12.A

A10.A

A8.A 35

A6.A 37

A4.A 39

A2.A 41

AO.A 43

AMB.A 45

GROUND 47

GROUND 49

50 -CLKOUT

-CRUCLK.A 51

GROUND 53

56 -MEMEN.A

CRUIN 55

-16V

+16V

(VIEW LOOKING INTO PBOX)

```

|   |  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |  | \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| - |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |  | and the state of t |

|   |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### SECTION C: PBOX CARD ELECTRONIC FEATURES

# 1.0 Introduction

Each peripheral card designed to be used with the PBox will have certain features that will not only allow the device to work properly, but will keep it from interfering with other devices and the computer. Due to the diverse nature of possible peripheral devices, not all of the following electronic features will be implemented on every device. The peripheral designer is responsible for insuring that his or her design utilizes the appropriate buffering and device selection techniques to prevent bus contention between devices.

# 2.0 <u>Interfacing Notes</u>

As noted previously, the PBox has two basic bus systems, memory and CRU. The CRU bus is used to control most peripherals, while the memory bus is used to transfer data to and from the peripheral. The CRU bus can also be used to transfer data to and from a peripheral, but a slower rate since the CRU bus transfers information at the rate of one bit per cycle, whereas the memory system transfers one byte (8 bits) each cycle.

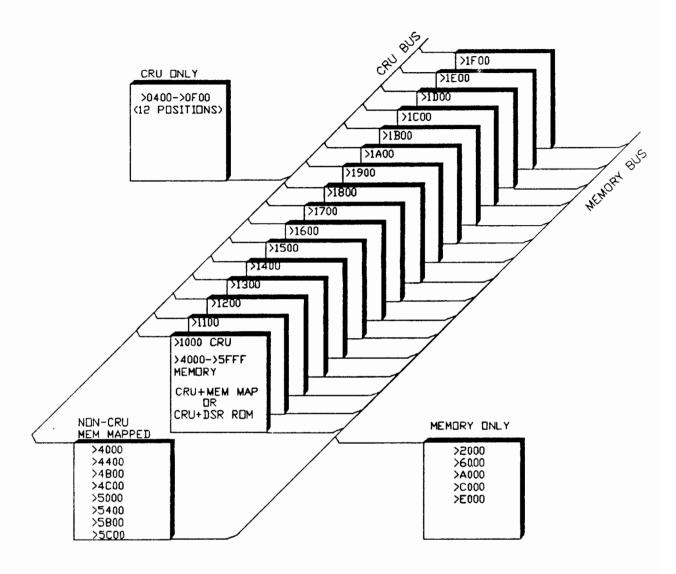

These two buses can be used in several designs to communicate between the computer and the peripheral. However, most interface designs can be grouped into one of five categories:

- 1) CRU only (serial)

- 2) Memory only

- 3) CRU and Memory Mapped (non-DSR)

- 4) CRU, DSR ROM, and Device

- 5) Non-CRU Memory Mapped

Each of these categories are discussed below. Note that the fourth category is the most common design, and the last category has not been defined until now.

### 2.1 CRU Only

In many ways, interfacing the computer to a peripheral via the CRU bus (only) is the simplist design of all. A peripheral that uses only the CRU bus to communicate has only one constraint: the CRU address(es) used by the peripheral must not be used by any other device. This is extremely important because most of the peripheral devices and the 9901 which drives the keyboard already have several CRU addresses assigned to them. Attempting to use any of these CRU addresses will result in contention on the CRU bus, and possible activation of other peripherals on the memory bus. [Following sections will explain how the CRU bus is used to poll and activate peripherals.] Section G contains the CRU map for the /4A. Each >0100 CRU address block has 128 addresses. Each peripheral space in the 16

locations reserved for peripheral devices (from >1000 to >1F00) has 128 CRU addresses available; however, usually no more than the first 8 CRU bits are used. The TMS9901 utilizes 32 CRU bits, starting at address >0000. The CRU space from >0400 to >0FFE is unassigned and has 12 sets of 128 CRU addresses available. It is recommended that peripherals based upon using the CRU bus only should be located within the >0400 to >0FFE CRU address range, with 128 bits available per CRU-only peripheral space. Table C.1 defines these twelve peripheral blocks. If more than 128 bits are required, then sequential peripheral blocks should be utilized. Any device that utilizes one or more of the peripheral blocks in Table C.1 shall have the CRU addresses clearly identified in the device documentation, and noted on the device itself, if possible. None of the CRU-only peripheral blocks are currently defined.

TABLE C.1 CRU-ONLY PERIPHERIAL BLOCKS

| ======= |                   |

|---------|-------------------|

| B1ock   | CRU Address Range |

| 1       | >0400->04FE       |

| 2       | >0500->05FE       |

| 3       | >0600->06FE       |

| 4       | >0700->07FE       |

| 5       | >0800->08FE       |

| 6       | >0900->09FE       |

| 7       | >0A00->0AFE       |

| 8       | >0B00->0BFE       |

| 9       | >0C00->0CFE       |

| 10      | >0D00->0DFE       |

| 11      | >0E00->0EFE       |

| 12      | >0F00->0FFE       |

|         |                   |

Note: While it is possbile to utilize CRU addresses within the sixteen polled peripheral spaces, it is not recommended since these bits may be used in existing or future devices. The twelve CRU-only peripheral blocks defined in Table C.1 should provide adequate space for development of these types of peripherals.

# 2.2 Memory Only

As seen in the /4A memory map, there is a total of 48K possible RAM space available, consisting of the following 8K blocks: >2000, >4000, >6000, >4000, >6000, >6000, >6000, >6000, and >6000. Utilization of these spaces is discussed below as they pertain to use in the PBox.

# 2.2.1 32K Design

The TI 32K RAM peripheral card covers the >2000 and >A000->FFFF memory spaces. Since the operating system of the /4A was designed to utilize RAM in these memory blocks, there is no need for special controls (such as CRU) to activate this memory device, only simple

address decoding. (See Section E.2 for more details.) The original TI memory card utilizes dynamic RAM; subsequent third party devices use more commonly available static RAM. Low power CMOS RAM is used in some designs along with batteries to retain data when the PBox power is off.

# 2.2.2 >4000 Space

The memory space from >4000 to >5FFF is reserved for paging in various peripheral devices and for memory mapped devices. See Sections 2.3 to 2.5.

# 2.2.3 >6000 Space

The space >6000->7FFF is traditionally not accessed from devices in the PBox because the /4A system assumes that it will be accessed from a cartridge in the 36 pin module port. The signal -ROMG on pin 34 is used to activate the 8K block at >6000. Bus contention will occur if a device in the PBox contains RAM/ROM at >6000, and a plug-in cartridge contains RAM/ROM/GROM at the same location. Peripheral devices containing memory in this 8K location are acceptable only if the memory is inactive upon powerup, and is activated by the user via hardware (switch) or software (CRU activation). This places the burden upon the user to activate this RAM space only after confirming that no module with memory in the >6000 space is inserted in the console. If software checking is used, a powerup routine that looks for "AA" at byte >6000 can be used to confirm that the space is not free for use.

#### 2.2.4 Bank Switching

Bank switching via CRU control is acceptable for the >2000, >6000 and >A000->FFFF memory spaces. However, most applications programs, especially BASIC utilizes these areas in predefined routines, particularily the >2000 block. Therefore, bank switched RAM blocks are useful for programs specifically designed to utilize them. As with other concepts, the designer must insure that two RAM blocks do not occupy the same address space simultaneously. Bank switching circuitry should be disabled by powerup or RESET activation.

#### 2.2.5 Extended Address Lines

The address lines AMA, AMB, and AMC are provided in the PBox bus to increase the linear address space of the system from 64K to 512K. As with bank switching, use of these lines to extend the available memory space is acceptable, but useful only for programs specifically designed to utilize them. A different interface card is required for the /4A system to allow use of AMA-AMC, since the card holds these signals high. Any memory device that uses these lines must make sure that AMA-AMC are high (=1) when accessing the "normal" 32K. Also, the designer should note that most of the TI produced peripheral cards are not activated if either AMA, AMB, or AMC are low.

### 2.2.6 Memory Mapping

An advanced technique for extending memory for peripherals is referred to as memory mapping. This technique is similar to bank switching, but utilizes a specialized LSI chip, the 74LS612 memory mapper to control generation of address lines beyond AO-A15. The '612 can be utilized to expand the address lines to accomodate up to 16 Meg bytes, without utilizing AMA-AMC. If a memory peripheral is designed to address more than 512K, then it is recommended that a memory mapper be located on the peripheral to generate local extended addresses for that device. [A description of the '612 and an application report is given in TI's "LSI Logic Data Book", 1986]

# 2.3 CRU Select and Memory Mapped (non-DSR ROM)

The /4A system is designed to sequentially poll 16 peripheral spaces, all located in the >4000 memory space. The CRU bus is used to select and activate these perpherials one at a time to prevent bus contention. The system and the 16 peripheral spaces are described in Section 4.0. This section covers memory mapped devices that are placed in one of the 16 polled peripheral spaces. These devices may or may not also have applications ROM/RAM; but it does not contain a valid Device Service Routine program. Section 2.5 covers memory mapped devices that are not polled by the /4A system, and do not have separate applications programs within their assigned memory space.

Memory mapped devices are accessed at only one address, or a small series of addresses. An existing example of a memory mapped device is the 9918A video chip. For the purposes of this section, it is assumed that these devices do not require a Device Service Routine (DSR) ROM to properly operate. An applications ROM or RAM of up to 8K length may be located within the same peripheral space, as long as it does not place the value "AA" in the first byte, and its assigned address range does not include the memory mapped address(es). This type of device may be activated by the /4A peripheral polling system, but will not respond since it does not have a valid DSR header. This type of peripheral is different from the standard polled peripheral, described in Section 4.0, in that it does not need a powerup, interrupt or applications program that uses the /4A polling and PAB access system, but does need valid addresses for memory mapped devices, and possibly an applications program to run. Since it would be located in the >4000 block, it can not be activated while the polled peripherals are being accessed.

For this type of peripheral, the following requirements must be met:

- a) The memory mapped device must be located in the range of >4002->5FFF; it cannot be located at either >4000 or >4001 since it might be accidently activated by the polling system.

- b) The memory mapped address(es) must not overlap with any ROM/RAM activated by this device.

- c) The memory mapped address decoder chips, data buffers and ROM/RAM select chips are to be activated only when that peripheral

space is selected by the CRU bus by the calling program, and be deactivated when the peripheral is not selected.

- d) The peripheral must be activated by writing a high CRU bit (=1) to the card, and deactivated by writing a low value (=0) to the same bit. To avoid spurious activation by the /4A polling system, it is recommended that the activation CRU bit not be at CRU bit 0 for that peripheral space.

- e) If the memory mapped device requires interrupts to communicate with the console, or a powerup/reset program, then it must have a valid DSR ROM (Section 2.4).

- f) Applications software must be provided to properly activate the peripheral and insure that it is deactivated when communication is complete. Due to potential bus contention from another interrupt driven peripheral (which would automatically activate the polling system), all interrupts should be suspended via a LIMI O command by the applications software, then restored when the device is deactivated.

- g) The device should utilize one of the peripheral spaces and its assigned CRU bit address range from the table in Section 4.0.

An example of this type of peripheral would be a Real Time Clock (RTC) that is periodically read by an applications program, and does not generate interrupts. The applications program would convert the RTC's output into the desired format, and place the time on the screen. When the applications program reads the RTC, or writes to set the time, external interrupts are suspended, the peripheral device is activated and accessed, then deactivated and interrupts are reactivated.

#### 2.4 CRU Select, Device and DSR ROM

This type of peripheral is similar to those described in Section 2.3, except that a ROM device with a valid DSR must be included for the device to properly respond to the /4A polling system. The software section of this manual covers requirements for creation of DSR software. ROM/RAM up to 8K in length may be located in the >4000->5FFF space, and must not overlap with any other device on the peripheral that is memory mapped or uses other address decoding schemes.

For this type of peripheral, the following requirements must be met:

- a) The DSR memory must be located starting at address >4000, and may extend to >5FFF.

- b) Permanent memory (ROM, PROM, EPROM, EEPROM) is recommended for holding the DSR. RAM may be used, if loaded after powerup. Use of RAM for holding the DSR prevents use of the peripheral until the DSR is loaded. Non-DSR RAM (for scratchpad or data storage) may be used as long as the total memory (DSR + non-DSR) is 8K or less.

- c) Any other devices on the peripheral must not share the same address space as the ROM/RAM.

- d) The DSR memory must be designed such that the data buffers,

DSR ROM/RAM select chips and any other device requiring address decoding are to be activated only when that peripheral space is selected by the /4A polling system. This system requires that the first CRU bit of that peripheral space activate the peripheral by writing a high value (=1) when it is selected, then deactivate the peripheral by writing a low value (=0) to the same CRU bit.

e) If the peripheral utilizes interrupts, then it must have an open collector driver connected to ground that can be cleared by the applications software once the peripheral is accessed.

An example of this type of peripheral is the RS232 cards, which are located at >1300 and >1500, and contain both DSR ROM and other chips, like the TMS9902 UART. See Section 4.0 for more details on how these peripherals are accessed by the /4A system.

# 2.5 Non-CRU Memory Mapped Devices